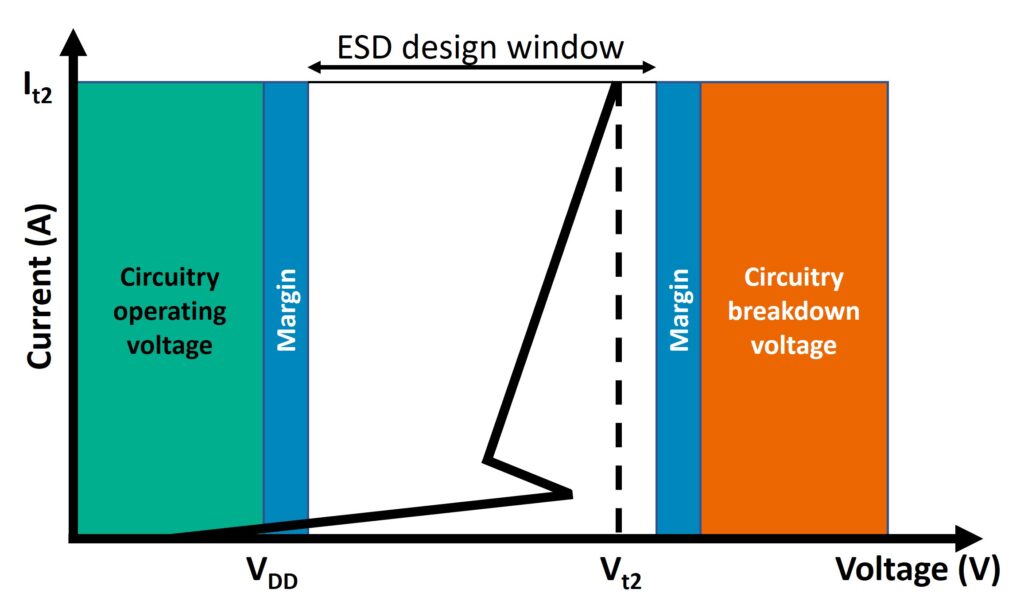

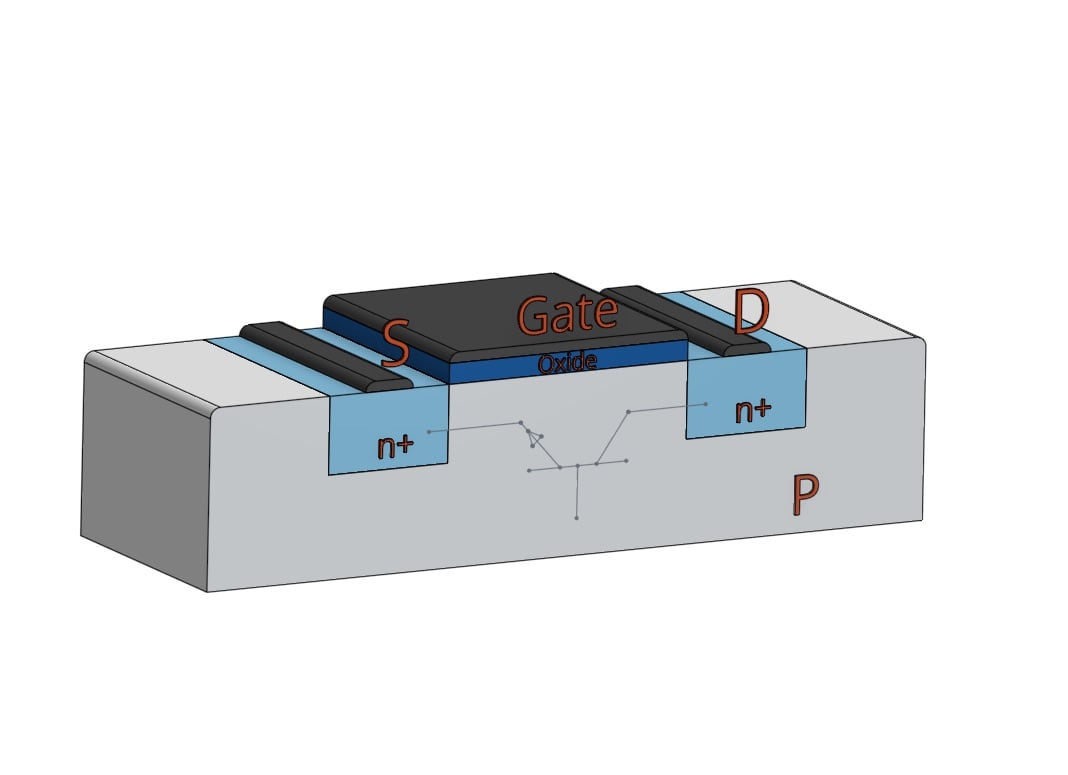

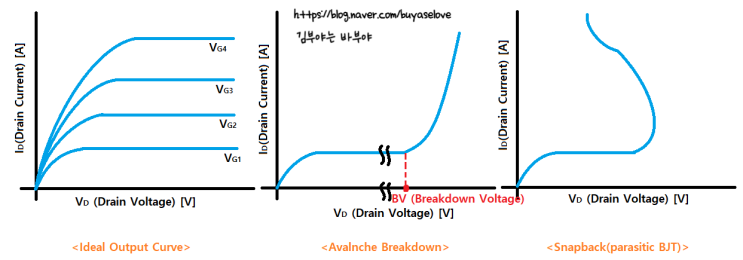

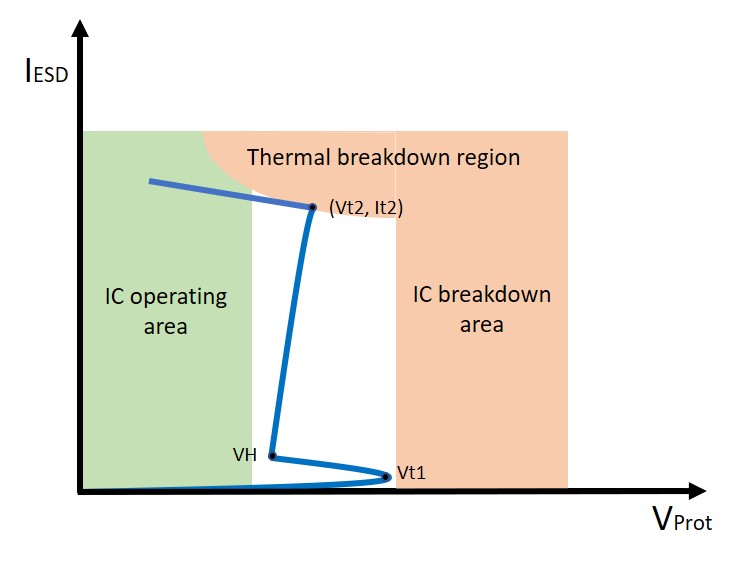

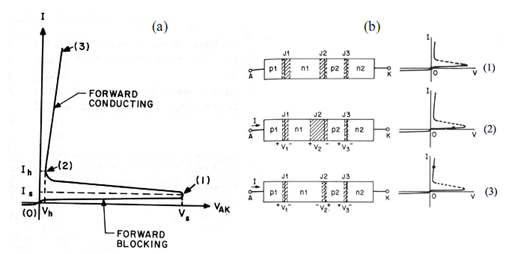

Bipolar effects in snapback mechanism in advanced n-FET transistors under high current stress conditions

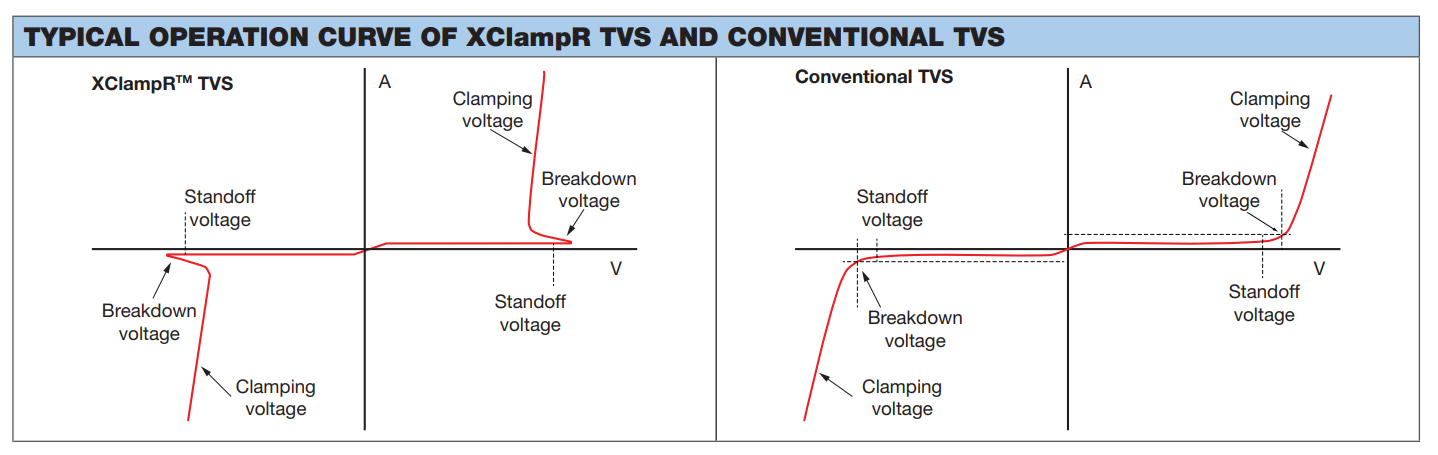

Snapback breakdown ESD device based on zener diodes on silicon-on-insulator technology - ScienceDirect

Bipolar effects in snapback mechanism in advanced n-FET transistors under high current stress conditions

Micromachines | Free Full-Text | A Snapback-Free and Low Turn-Off Loss 15 kV 4H–SiC IGBT with Multifunctional P-Floating Layer

Bipolar effects in snapback mechanism in advanced n-FET transistors under high current stress conditions

Modeling MOS snapback and parasitic bipolar action for circuit-level ESD and high current simulations | Semantic Scholar

PDF) Measurement on snapback holding voltage of high-voltage LDMOS for latch-up consideration | Ming-dou Ker - Academia.edu